- Autor Lynn Donovan donovan@answers-technology.com.

- Public 2023-12-15 23:42.

- Zuletzt bearbeitet 2025-01-22 17:14.

VHDL und Verilog gelten als universelle digitale Designsprachen, während SystemVerilog eine erweiterte Version von. darstellt Verilog . VHDL hat Wurzeln in dem Ada-Programmiersprache sowohl im Konzept als auch in der Syntax, während Verilogs Wurzeln können bis zu einem frühen HDL namens Hilo und der Programmiersprache C zurückverfolgt werden.

Die Leute fragen auch, was ist besser VHDL oder Verilog?

VHDL ist ausführlicher als Verilog und es hat auch eine Nicht-C-ähnliche Syntax. Mit VHDL , haben Sie eine höhere Chance, mehr Codezeilen zu schreiben. Verilog hat ein besser Verständnis für die Hardwaremodellierung, hat aber eine niedrigere Ebene von Programmierkonstrukten. Verilog ist nicht so ausführlich wie VHDL Deshalb ist es kompakter.

Und was nützt Verilog? Verilog ist eine Hardwarebeschreibungssprache; ein Textformat zur Beschreibung elektronischer Schaltungen und Systeme. Angewandt auf elektronisches Design, Verilog soll zur Verifikation durch Simulation, zur Timing-Analyse, zur Testanalyse (Testbarkeitsanalyse und Fehlerbewertung) und zur Logiksynthese verwendet werden.

Was ist auf diese Weise der Unterschied zwischen Verilog und SystemVerilog?

Das Wichtigste Unterschied zwischen Verilog undSystemVerilog ist dass Verilog ist eine Hardware-Beschreibungssprache, während SystemVerilog ist eine Hardwarebeschreibungs- und Hardwareverifizierungssprache basierend auf Verilog . In Kürze, SystemVerilog ist eine erweiterte Version von Verilog mit zusätzlichen Funktionen.

Was ist VHDL in VLSI?

VLSI Entwurf - VHDL Einführung. Werbung. VHDL steht für sehr schnelle Hardwarebeschreibungssprache für integrierte Schaltungen. Es ist eine Programmiersprache, die verwendet wird, um ein digitales System durch Datenfluss, Verhaltens- und Strukturmodellierungsstil zu modellieren.

Empfohlen:

Was ist der Unterschied zwischen der Gesamtberichts- und der Teilberichtsbedingung?

Bei nicht zusammenhängenden Items in einer Liste (wie in den Experimenten von Nieuwenstein & Potter, 2006) wird der gesamte Bericht von der Gesamtzahl der Items in einer Sequenz beeinflusst, während ein Teilbericht nur minimal von der Gesamtzahl der Items beeinflusst wird, wenn nur zwei sein sollen gemeldet

Was ist der Unterschied zwischen der Ausführung von config und der Startkonfiguration?

Eine laufende Konfiguration befindet sich im RAM eines Geräts. Wenn also ein Gerät mit Strom versorgt wird, gehen alle konfigurierten Befehle verloren. Eine Startkonfiguration wird im nichtflüchtigen Speicher eines Geräts gespeichert, dh alle Konfigurationsänderungen bleiben auch bei einem Stromausfall des Geräts erhalten

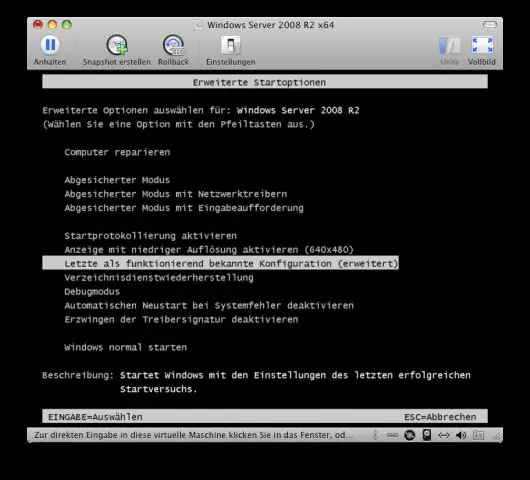

Was ist der Unterschied zwischen der letzten als funktionierend bekannten Konfiguration und der Systemwiederherstellung?

Während die Systemwiederherstellung Wiederherstellungspunkte verwendet, um Ihre Systemdateien und Einstellungen auf einen früheren Zeitpunkt zurückzusetzen, ohne persönliche Dateien zu beeinträchtigen. Sie können die Systemwiederherstellung rückgängig machen, aber in der letzten als funktionierend bekannten Konfiguration gibt es keine solche Option. Letzte als funktionierend bekannte Konfiguration ist in Windows 8 oder Windows 8.1 standardmäßig deaktiviert

Was ist der Unterschied zwischen der Zwischenablage und der Office-Zwischenablage?

Die Office-Zwischenablage kann die letzten 24 kopierten Elemente beibehalten. Die Office-Zwischenablage sammelt auch eine Liste kopierter Elemente aus mehreren Dokumenten in einem beliebigen Office-Programm, die Sie als Gruppe in ein anderes Office-Programmdokument einfügen können

Was ist der Unterschied zwischen der Facebook-App und der Facebook Lite-App?

Facebook Lite unterscheidet sich von Facebook für Android für iOS dadurch, dass es: nur die wichtigsten Facebook-Funktionen hat. Verbraucht weniger mobile Daten und nimmt weniger Speicherplatz auf Ihrem Mobiltelefon ein. Funktioniert gut in allen Netzwerken, einschließlich 2G